Professor Eliathamby Ambikairajah

Head of School of Electrical Engineering and Telecommunications, UNSW, Sydney

# **Analogue to digital Converter (ADC) Module**

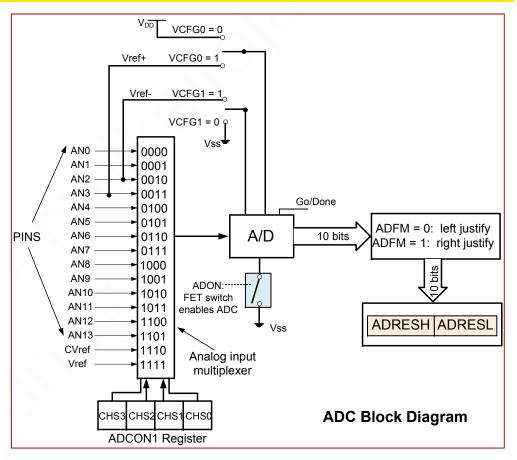

- ✓ The Analogue to Digital Converter allows conversion of an analogue input signal to a 10-bit binary representation of that signal.

- The conversion result of the ADC is stored in the registers ADRESL (contains low byte conversion result) and ADRESH (contains high byte conversion result).

- ✓ There are 14 separate analogue inputs which are multiplexed in order to select the appropriate input to the ADC

- ✓ The ADC voltage reference is software selectable to either V<sub>DD</sub> or a voltage applied to the external reference pins

- The ADC can generate an interrupt upon completion of a conversion or Polling

A/D acquisition Requirements: After selecting (or changing) the analogue input and before starting conversion it is necessary to provide at least 20 µs time delay to enable the ADC module (A/D converter module) to provide maximal conversion accuracy.

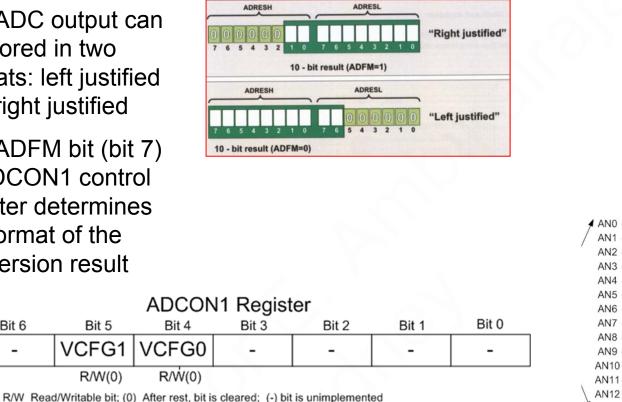

## **ADRESH and ADRESL Registers**

- ✓ The ADC output can be stored in two formats: left justified and right justified

- $\checkmark$  The ADFM bit (bit 7) of ADCON1 control register determines the format of the conversion result

Bit 6

Bit 7

ADFM

R/W(0)

- 1 conversion result right justified; six most significant bits of the ADRESLH are not used

- 0 Conversion result is left justified. Six least significant bits of the ADRESL are not used.

VCFG1 – Voltage Reference bit selects negative voltage reference source needed for A/D converter operating

1 – Negative voltage reference is applied on the Vref- pin

Bit 5

R/W(0)

VCFG1

0 – Voltage power supply VSS is used as negative voltage reference source

**VCFG0** – Voltage Reference bit selects positive voltage reference source needed for A/D converter operating

- 1 positive voltage reference is applied on the Vref+ pin

- 0 Voltage power supply VDD is used as positive voltage reference source

Go

A/D

Vss

VDD

Vref+

Vref-

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

ΔN13

VCFG0 = 0

VCFG0 = 1

VCFG1 = 1,

VCFG1 = 0 9

Vss\*

ADON:

FET switch

enables ADC

## **Channel selection**

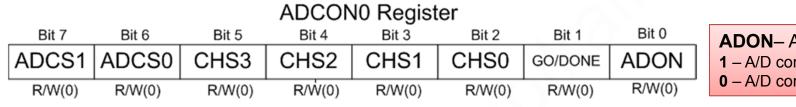

✓ The CHS bits of the ADCON0 control register determine which channel is connected to the A/D converter (ie connected to the Sample and Hold circuit)

ADON – A/D enable bit

1 – A/D converter is enabled

0 – A/D converter is disabled

R/W Read/Writable bit; (0) After rest, bit is cleared;

**ADCS1, ADCS0** – A/D conversion Clock select bits. Select clock frequency used for internal synchronisation of A/D converter. It also affects the duration of conversion **GO/DONE:** A/D conversion status bit determines current status of conversion;

- 1-A/D conversion is in progress;

- **0** A/D conversion is complete

| ADCS1 | ADCS2 | Clock                |

|-------|-------|----------------------|

| 0     | 0     | F <sub>osc</sub> /2  |

| 0     | 1     | F <sub>osc</sub> /8  |

| 1     | 0     | F <sub>osc</sub> /32 |

| 1     | 1     | F <sub>RC</sub> *    |

CHS0 to CHS3: Analogue select bits \_\_\_\_\_ select a pin/analogue channel for analogue to digital conversion

$F_{RC}^*$  = clock derived from a dedicated internal oscillator = 500kHz max)

There are 14 analogue input select pins available: PA0 to PA5, PE0 to PE2 and PB0 to PB5 (Ports A, B and E)

| CHS3          |   | CHS2 | CHS1 | CHS0 | Channel | Pin      |  |  |  |

|---------------|---|------|------|------|---------|----------|--|--|--|

|               | 0 | 0    | 0    | 0    | 0       | RA0/AN0  |  |  |  |

|               | 0 | 0    | 0    | 1    | 1       | RA1/AN1  |  |  |  |

|               | 0 | 0    | 1    | 0    | 2       | RA2/AN2  |  |  |  |

| $\rightarrow$ | 0 | 0    | 1    | 1    | 3       | RA3/AN3  |  |  |  |

|               | 0 | 1    | 0    | 0    | 4       | RA5/AN4  |  |  |  |

|               | 0 | 1    | 0    | 1    | 5       | RE0/AN5  |  |  |  |

|               | 0 | 1    | 1    | 0    | 6       | RE1/AN6  |  |  |  |

|               | 0 | 1    | 1    | 1    | 7       | RE2/AN7  |  |  |  |

|               | 1 | 0    | 0    | 0    | 8       | RB2/AN8  |  |  |  |

|               | 1 | 0    | 0    | 1    | 9       | RB3/AN9  |  |  |  |

|               | 1 | 0    | 1    | 0    | 10      | RB1/AN10 |  |  |  |

|               | 1 | 0    | 1    | 1    | 11      | RB4/AN11 |  |  |  |

|               | 1 | 1    | 0    | 0    | 12      | RB0/AN12 |  |  |  |

|               | 1 | 1    | 0    | 1    | 13      | RB5/AN13 |  |  |  |

|               | 1 | 1    | 1    | 0    | C       | Vref     |  |  |  |

|               | 1 | 1    | 1    | 1    | Vref    | = 0.6V   |  |  |  |

## **A/D Conversion Procedure**

### ✓ Configure the port:

- Write logic one to the corresponding bit of the TRIS register to configure it as input;

- Write logic one to the corresponding bit of the ANSEL register to configure it as analog input.

#### ✓ Configuring ADC module:

- ✓ Configure voltage reference in the ADCON1 register;

- ✓ Select ADC conversion clock in the ADCON0 register

- ✓ Select one of the input channels CH0-CH13 of the ADCON0 register

- ✓ Select data format using the ADFM bit of the ADCON1 register

- ✓ Enable A/D converter by setting the ADCON bit of the ADCON0 register

- ✓ Configuring ADC Interrupt (optional):

- ✓ Clear ADIF bit (interrupt flag)

- ✓ Set the ADIE, PEIE and GIE bits (enable ADC, peripheral and Global interrupts)

#### $\checkmark$ Wait for the Required acquisition time (approx 20 µs) to pass

✓ Start conversion by setting the GO/DONE bit of the ADCON0 register – if GO/DONE bit is set, the A/D conversion will start

#### ✓ Wait for ADC conversion to complete by one of the following :

- ✓ Check in program loop to see if the GO/DONE bit is cleared (completion of a conversion)

- ✓ Wait for an A/D interrupt

- ✓ Read ADC results (i.e. read the ADRESH and ADRESL registers)

- ✓ Clear the ADC interrupt flag (required if interrupt is enabled)

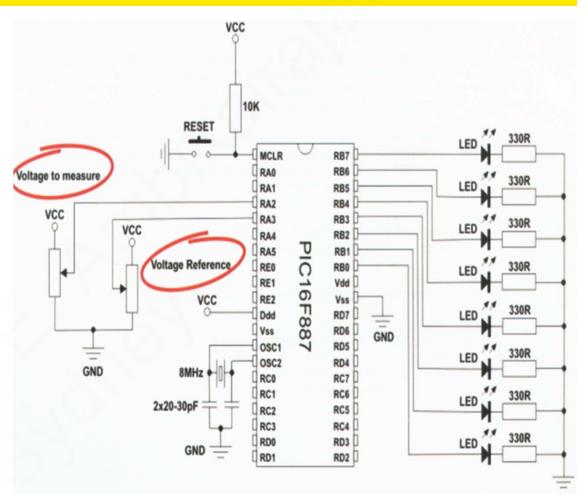

### **A/D Converter Example 1**

✓ Variable analogue signal is applied on the AN2 (PA2) pin while the result of conversion is shown on PORTB as binary number.

✓ A positive reference voltage is applied to the AN3 (PA3) pin.

✓ Difference between two voltage levels is converted to a binary (10 bit ) number.

✓ Only 8 lower bits of the result of conversion are shown.

## **A/D Converter Program**

|             | ANKSEL                                             | TRISB                                                  |                                                           |                                                                                                                                             |  |  |  |  |  |  |

|-------------|----------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| cl<br>m     | irt<br>ìovlw                                       | TRISB<br>B'00001100'                                   | ;all portB pins are output                                |                                                                                                                                             |  |  |  |  |  |  |

| m           | novwf                                              | TRISA                                                  | ;pins PA2 and PA3 as configured as ir                     | nputs                                                                                                                                       |  |  |  |  |  |  |

| B           | ANKSEL                                             | ANSEL                                                  |                                                           |                                                                                                                                             |  |  |  |  |  |  |

| m           | novlw                                              | B'00001100'                                            | ;inputs AN2 and AN3 are analogue while others are digital |                                                                                                                                             |  |  |  |  |  |  |

| m<br>cl     | novwf<br>Irf                                       | ANSEL; To configure a pi<br>ANSELH; set the port B li  | n as an analog input, the appropriate b                   | bit of the ANSEL must be set to 1                                                                                                           |  |  |  |  |  |  |

| CI          |                                                    | ANSELIT, Set the port Bill                             |                                                           | Right Justified                                                                                                                             |  |  |  |  |  |  |

| B           | ANKSEL                                             | ADCON1                                                 |                                                           | ADRESH ADRESL                                                                                                                               |  |  |  |  |  |  |

| bs          |                                                    | ADCON1,ADFM                                            | ; right justification of result>                          |                                                                                                                                             |  |  |  |  |  |  |

|             | cf                                                 | ADCON1,VCFG1                                           | ;Voltage Vss (GND) is used as Vref-                       |                                                                                                                                             |  |  |  |  |  |  |

| DS          | sf                                                 | ADCON1,VCFG0                                           | ;RA3 pin voltage is used as Vref+                         | 10 - bit result (ADFM=1)                                                                                                                    |  |  |  |  |  |  |

| B           | BANKSEL                                            | ADCON0                                                 |                                                           |                                                                                                                                             |  |  |  |  |  |  |

| m           | novlw                                              | B'00001001'                                            | ;A/D converter uses clock Fosc/2                          |                                                                                                                                             |  |  |  |  |  |  |

| m           | novwf                                              | ADCON0                                                 | ;on RA2 pin is used for conversion an                     | nd A/D converter is enabled                                                                                                                 |  |  |  |  |  |  |

|             |                                                    | N1 Register                                            |                                                           |                                                                                                                                             |  |  |  |  |  |  |

| Bit 7 Bit 6 | Bit 5 Bit 4<br>CFG1 VCFG0                          | Bit 3 Bit 2 Bit 1 Bit 0                                |                                                           | VDD VCFG0 = 0                                                                                                                               |  |  |  |  |  |  |

|             | R/W(0) R/W(0)<br>itable bit; (0) After rest, bit i | s cleared; (-) bit is unimplemented                    |                                                           | RB7 - Vref+ VCFG0 = 1                                                                                                                       |  |  |  |  |  |  |

|             |                                                    | N0 Register                                            | RA1                                                       | RB5 D-                                                                                                                                      |  |  |  |  |  |  |

| Bit 7 Bit 6 | Bit 5 Bit 4                                        | Bit 3 Bit 2 Bit 1 Bit 0                                | VCC RA3                                                   |                                                                                                                                             |  |  |  |  |  |  |

|             | CHS3 CHS2                                          | CHS1 CHS0 GO/DONE ADON                                 | VCC CRA4                                                  |                                                                                                                                             |  |  |  |  |  |  |

| () ()       | R/W(0) R/W(0)<br>W Read/Writable bit; (0) A        | R/W(0) R/W(0) R/W(0) R/W(0) fter rest, bit is cleared; | Voltage Reference                                         | RB1 ANO 0000<br>AN1 0001                                                                                                                    |  |  |  |  |  |  |

| ADCS1 ADCS2 | 2 Clock                                            |                                                        |                                                           | Vdd AN2 0010<br>AN3 0011                                                                                                                    |  |  |  |  |  |  |

| 0 0         | F <sub>osc</sub> /2                                | ADON- A/D enable bit                                   |                                                           | RD7 AN5 -0101                                                                                                                               |  |  |  |  |  |  |

| 0 1         | F <sub>osc</sub> /8                                | 1 – A/D converter is enabled                           |                                                           | RD6         AN6         0110         A/D           RD5         AN7         0111         0111           AN8         1000         0         0 |  |  |  |  |  |  |

| 1 0         | F <sub>osc</sub> /32                               | 0 – A/D converter is disabled                          | -                                                         | AN8 1000                                                                                                                                    |  |  |  |  |  |  |

| 1 1         | F <sub>RC</sub> *                                  |                                                        |                                                           |                                                                                                                                             |  |  |  |  |  |  |

|                                              | A/D Converter Program contd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| call                                         | acquisition_delay ; Delay of 20 µs<br>Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0<br>ADCON0 Register<br>Bit 4 Bit 3 Bit 2 Bit 1 Bit 0<br>ADCN0 Register<br>ADCON0 Re |

| BANKSEL<br>bsf                               | 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0 201/0                                                                                                                                                                                                                                         |

| loop nop<br>btfsc<br>goto<br>BANKSEL<br>movf | ADCON0,1 ;Tests bit Go/Done; Is this bit = 0 (at the end of A/D conversion ADC module clears this bit)<br>loop ; conversion in progress, stay in loop<br>;At the end of conversion ADRESH:ADRESL registers are updated with the new<br>;conversion result<br>ADRESL<br>ADRESL,w ;lowerbyte of conversion result is copied to W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| banksel<br>movwf<br>bsf<br>goto<br>END       | PORTB<br>PORTB ;byte is copied to PORTB<br>ADCON0,1 ;starts new conversion<br>loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

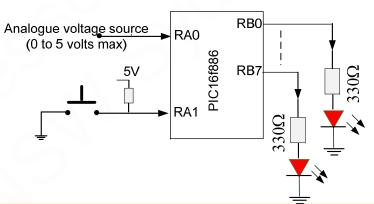

## A/D Converter Example 2

An analogue voltage source is connected to AN0 (RA0) of PORTA of a PIC16F886 microcontroller which is set up to sample the analogue signal and stores the 10 bit digital output in the locations 'DIGITALHI' (upper two bits) and 'DIGITALLO' (lower 8 bits). You need to configure the ADC for polling, V<sub>DD</sub> and V<sub>SS</sub> as reference, select F<sub>RC</sub> clock and AN0 as analogue input.

VCFG0 = 1

• Write an assembly program to achieve the above.

|         |        |     |            | 011 -          | 5.4.0    | <b>D</b> 14 F | ADCON      |          |           | 511.4         | Dit O         |                         | Vref-                      | VCFG1 = 1        | <b>_</b>     |    |

|---------|--------|-----|------------|----------------|----------|---------------|------------|----------|-----------|---------------|---------------|-------------------------|----------------------------|------------------|--------------|----|

|         | ITALHI | equ | H'20'      | Bit 7          | Bit 6    | Bit 5         | Bit 4      | Bit 3    | Bit 2     | Bit 1         | Bit 0         |                         |                            | VCFG1 = 0 0      |              |    |

| DIG     | ITALLO | equ | H'21'      | R/W(0)         | -        | R/W(0)        | R/Ŵ(0)     | -        | -         | -             | -             | AN0 -                   | + 0000                     |                  |              |    |

| BAN     | NKSEL  |     | ADCON1     | 1011(0)        |          | 1011(0)       | 1011(0)    |          |           |               |               | AN2 -<br>AN3 -          | 0001                       |                  |              | 60 |

| MO      | VLW    |     | B'1000000' | ; result right | justifie | d ADFM        | =1         |          |           |               |               | AN4 -<br>AN5 -          | + 0100<br>+ 0101           |                  |              | Ť  |

| MO      | VWF    |     | ADCON1     | ;VCFG1=0 (     | select ' | Vss – gr      | ound); V   | CFG0=    | =0 (seled | ct VDD)       |               | AN6 -<br>AN7 -<br>AN8 - | + 0110<br>+ 0111<br>+ 1000 | 1 L              | A/D          | ┢  |

| BAN     | NKSEL  |     | TRISA      |                |          |               |            |          |           |               |               | 7.100                   | 11000                      | I                |              |    |

| BSF     | F      |     | TRISA,0    | ; Set RA0 to   | input    |               |            |          |           |               |               |                         |                            |                  |              |    |

| BAN     | NKSEL  |     | ANSEL      |                |          |               |            |          | 87.0      | 0.1           |               | N0 Regist               |                            | <b>D</b> 14 4    | DHO          |    |

| BSF     | F      |     | ANSEL,0    | ; Set RA0 to   | analog   | gue           |            | Bit 7    |           | Bit 5<br>CHS3 | Bit 4<br>CHS2 | Bit 3<br>CHS1           | Bit 2<br>CHS0              | Bit 1<br>GO/DONE | Bit 0<br>ADO |    |

| BAN     | NKSEL  |     | ADCON0     |                |          |               |            | R/W(0    | ) R/W(0)  | R/W(0)        | R/Ŵ(0)        | R/W(0)                  | R/W(0)                     | R/W(0)           | R/W(0        | )) |

| МО      | VLW    |     |            | ; FRC clock:   | ADCS     | 1=1; AD       | CS0 =1;    | CHS0     | to CHS    | 3 = 0 (s      | elect A       | N0 for                  | A/D co                     | nversio          | on)          |    |

| МО      | VWF    |     | ADCON0     | ; ADON=1 (A    | VD co    | nverter i     | s enable   | d)       |           |               |               |                         |                            |                  |              |    |

| CAI     | LL     |     | Delay      | ; Delay of 20  |          |               |            | ,        |           |               |               |                         |                            |                  |              |    |

| BSF     | F      |     | ADCON0,1   | ; start conve  | rsion b  | y setting     | GO/DC      | NE bit   |           |               |               |                         |                            |                  |              |    |

| LOOP NO | P      |     |            |                |          |               |            |          |           |               |               |                         |                            |                  |              |    |

| BTF     | FSC    |     | ADCON0,1   | ;Tests bit Go  | /Done    | Is this b     | oit = 0 (a | t the er | nd of A/E | ) conve       | rsion A       | DC mo                   | odule c                    | lears th         | nis bi       | t) |

| GO      | ОТО    |     | LOOP       | ; No try agaii | า        |               |            |          |           |               |               |                         |                            |                  |              | •  |

| BAN     | NKSEL  |     | ADRESH     |                |          |               |            |          |           |               |               |                         |                            |                  |              |    |

| МО      | VF     |     | ADRESH,w   | ;Read upper    | two bi   | ts            |            |          |           |               |               |                         |                            |                  |              |    |

| МО      | VWF    |     | DIGITALHI  | ; store in me  |          |               |            |          |           |               |               |                         |                            |                  |              |    |

| BAN     | NKSEL  |     | ADRESL     |                |          |               |            |          |           |               |               |                         |                            |                  |              |    |

| МО      | VF     |     | ADRESL,w   | ;Read lower    | 8 bits   |               |            |          |           |               |               |                         |                            |                  |              |    |

|         | VWF    |     |            | ; store in me  |          |               |            |          |           |               |               |                         |                            |                  |              |    |

| ENI     |        |     |            | -              |          |               |            |          |           |               |               |                         |                            |                  |              | 8  |

### **Laboratory Activity**

### Activity 9: Analogue to Digital conversion

- A variable analogue voltage source is connected to PA0 (RA0) of PORTA of a PIC16F886 microcontroller and a switch is connected to PA1(RA1) of PORTA of the same microcontroller.

- Write an assembly code such that when the switch is pressed (high-to-low transition), the microcontroller samples the analogue input and the result of the conversion is shown as an 8-bit binary number on PORTB. Only the least significant 8-bits (of the 10-bit ADC) need to be displayed using the eight LEDs connected to PORTB.

- You need to clear VCFG1, VCFG0, ADSC0 and ADSC1 for the desired operation of the ADC module.

- You need to write a 20µs acquisition delay sub-routine (acquisition\_delay) for you to call in your code. That is, after selecting (or changing) the analogue input and before starting conversion it is necessary to provide at least 20 µs time delay to enable the ADC module to provide maximal conversion accuracy.

### **ELEC2117: References**

- 1. Designing Embedded Systems with PIC Microcontrollers Tim Wilmshurst, Elsevier, 2010

- 2. PIC Microcontrollers –Free online book mikroElektronika ; http://www.mikroe.com/products/view/11/book-pic-microcontrollers/

- 3. PIC 16F886 Data Sheet (2007), Microchip Technology; www.microchip.com