Professor Eliathamby Ambikairajah

Head of School of Electrical Engineering and Telecommunications, UNSW, Sydney

#### Timers

- ✓ There are three completely independent timers/counters available in PIC16f886 micro controllers and they are marked as TMR0, TMR1 and TMR2

- TMR0 has a wide range of applications in practice: (a) Time measurement

(b) Counting external pulses (c) Generating pulses of arbitrary duration

- TMR0 operation: When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter

- ✓ Timer0 appears as register TMR0 at memory location H'01' in data memory bank 0

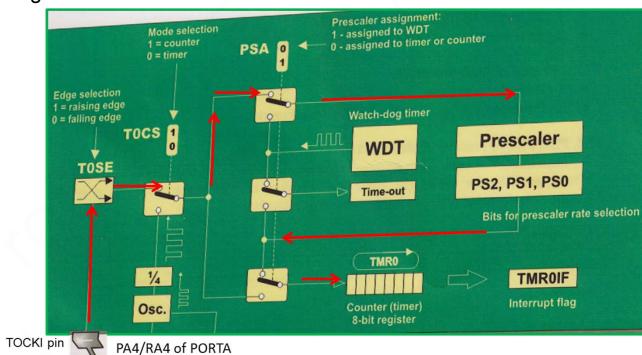

- TMR0 is configurable and controlled by a number of bits that appear in the OPTION register

00H (INDF) 01H TMR0 03H STATUS 04H FSR OBH INTCON 0CH PIR1 0DH PIR2 0EH TMR1L GPR 20H Bank 0

#### Timers

- ✓ When used as a 8-bit timer, the Timer0 module will increment every instruction cycle.

- Timer mode is selected by clearing the TOCS bit (bit5) of OPTION register to '0'

- ✓ When used as a 8-bit counter, the Timer0 module will increment on every rising or falling edge of the TOCKI pin (PA4/RA4 of PORTA).

- The incrementing edge is determined by the T0SE bit of the OPTION register.

- The counter mode is selected by setting the T0CS bit (bit5) of Option register to '1'.

|        |        |        | in iteyisid |        | emory bank i | anu s  |        |

|--------|--------|--------|-------------|--------|--------------|--------|--------|

| Bit 7  | Bit 6  | Bit 5  | Bit 4       | Bit 3  | Bit 2        | Bit 1  | Bit 0  |

| RBPU   | INTEDG | TOCS   | TOSE        | PSA    | PS2          | PS1    | PS0    |

| R/W(1) | R/W(1) | R/W(1) | R/W(1)      | R/W(1) | R/W(1)       | R/W(1) | R/W(1) |

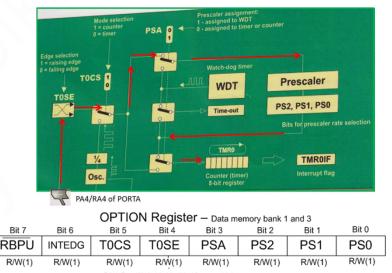

#### OPTION Register - Data memory bank 1 and 3

R/W Read/Writable bit; (1) After rest, bit is set;

TOCS - TMR0 Clock Select bit

- 1 Transition on TOCK1 pin (PA4/RA4 of PORTA); i.e clock mode

- 0 Internal instruction cycle clock (Fosc/4) i.e timer mode

**TOSE** – TMR0 Source Edge Select bit

- 1 increment on high to low transition on TOCKI pin;

- **0** increment on low to high transition on TOCKI pin;

# **Option Register**

|                                                                                                                                                 |                |             | OPTIO     | N Registe         | e <b>r —</b> Data m | emory b | ank 1 a | nd 3   |       |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-----------|-------------------|---------------------|---------|---------|--------|-------|------|

|                                                                                                                                                 | Bit 7          | Bit 6       | Bit 5     | Bit 4             | Bit 3               | Bit     | 2       | Bit 1  | Bit   | 0    |

|                                                                                                                                                 | RBPU           | INTEDG      | T0CS      | T0SE              | PSA                 | PS:     | 2       | PS1    | PS    | 0    |

|                                                                                                                                                 | R/W(1)         | R/W(1)      | R/W(1)    | R/W(1)            | R/W(1)              | R/W     | /(1)    | R/W(1) | R/W   | (1)  |

|                                                                                                                                                 |                |             | R/W Read/ | Writable bit; (1) | After rest, bit is  | set;    |         |        |       |      |

| <b>RBPU</b> – PORTB Pull-up Enable bit      1 – PORTB pull-ups are disabled      0 – PORTB pull-ups are enabled by individual PORT latch values |                |             |           |                   |                     |         |         |        |       |      |

| PSA – Prescaler Assignment bit      1 – Prescaler is assigned to the WDT (watchdog Timer);      0 – Prescaler is assigned to the Timer0 module  |                |             |           |                   |                     |         |         |        | TMR0  | WDT  |

|                                                                                                                                                 |                |             |           |                   |                     | 0       | 0       | 0      | 1:2   | 1:1  |

|                                                                                                                                                 |                | nalar Data  |           |                   |                     | 0       | 0       | 1      | 1:4   | 1:2  |

| •                                                                                                                                               | •              | scaler Rate |           |                   | 0                   | 1       | 0       | 1:8    | 1:4   |      |

| •                                                                                                                                               | requency divis |             | 0         | 1                 | 1                   | 1:16    | 1:8     |        |       |      |

|                                                                                                                                                 |                |             |           |                   |                     | 1       | 0       | 0      | 1:32  | 1:16 |

|                                                                                                                                                 |                |             |           |                   |                     | 1       | 0       | 1      | 1:64  | 1:32 |

|                                                                                                                                                 |                | 90          |           |                   |                     | 1       | 1       | 0      | 1:128 | 1:64 |

|                                                                                                                                                 |                |             |           |                   |                     |         |         |        |       |      |

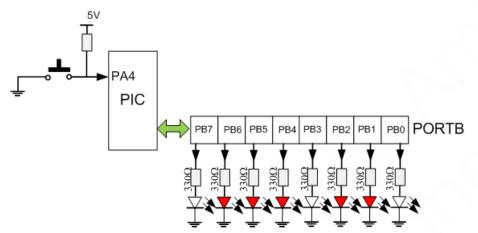

# **TMR0: Counter Mode**

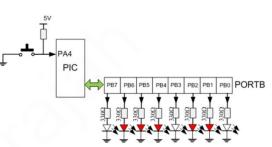

- > A push button is connected to the PA4 pin of PORTA as shown in the diagram below.

- Write an assembly language program to continuously count (use TMR0 to count the pulses) the pressing and releasing of the button (one count) and continuously display the counter value on the LEDs connected to PORTB.

- > You may assume that the switch is debounced.

- To configure Timer0 we need to select its external input (i.e TOCS of Option Reg must be 1)

- We will count at the rising edge (i.e TOSE of the Option Reg must be 0) I

- We do not want the prescaler as we want to count the exact number of switch presses. i.e PSA of the Option Reg = 1; Hence the values of PS2, PS1, PS0 do not matter as we do not need WDT in this program.

- The final value of the Option Reg is B'00101000'

R/W(1)

R/W(1)

#### ; Event Counting using Timer0

;Intialisation

| start           | BANKSEL<br>clrf<br>clrf | ANSEL<br>ANSEL<br>ANSELH | ;set PO     | RTA to d  | bank cor<br>ligital by<br>b digital b | clearing   | ANSEL              | Register    |           |              | 00H            | Indirect<br>address<br>(INDF) |

|-----------------|-------------------------|--------------------------|-------------|-----------|---------------------------------------|------------|--------------------|-------------|-----------|--------------|----------------|-------------------------------|

|                 | CIT                     | ANGLEH                   | ,501 P O    |           | ulgital t                             | y clean    | IN ANOL            | LITILEY     | 15101     |              | 0411           |                               |

| ,               |                         |                          | ia ala at r | ~~~~      | hankaar                               | toining .  |                    |             |           | - <b>r</b> - | 01H            | TMRO                          |

|                 | BANKSEL                 | TRISA                    |             |           | bank cor                              | naming     | IRISAa             |             | D Regisi  | ers          | 02H            | PCL                           |

|                 | movlw                   | B'00010000'              | ;PA4 =1     |           |                                       |            |                    |             |           |              | 03H            | STATUS                        |

|                 | movwf                   | TRISA                    |             |           | (PA4 as i                             | • •        |                    |             |           |              | 04H            | FSR                           |

|                 | clrf                    | TRISB                    |             |           | all output                            |            |                    |             |           |              | 05H            | PORTA                         |

|                 | BANKSEL                 | PORTB                    | ;select r   | nemory    | bank cor                              | ntaining   | PORTA a            | and POF     | RTB       |              | 06H            | PORTB                         |

|                 |                         |                          | ;Registe    | ers       |                                       |            |                    |             |           |              | 07H            | PORTC                         |

|                 | clrf                    | PORTB                    | ;reset P    | ORTB (t   | urn off a                             | ll LEDS)   |                    |             |           |              | 20H:           | (GPR)                         |

|                 | clrf                    | TMR0                     | ;As we a    | are in Ba | ank 0, we                             | e may as   | well cle           | ar the co   | ontents o | f the        | 7FH            | 96 Bytes                      |

|                 |                         |                          | ;Timer0     |           |                                       |            |                    |             |           |              |                | Bank 0                        |

|                 |                         |                          |             |           |                                       |            |                    |             |           |              |                |                               |

|                 | BANKSEL                 | OPTION_RE                | G ;selec    | t Option  | register                              | to use T   | MR0                |             |           |              | 180H           | Indirect                      |

|                 | Movlw                   | B'00101000'              |             |           | or externa                            |            |                    | S=1) inp    | out and n | 0            | 4.0411         | address                       |

|                 |                         |                          | :Presca     |           |                                       | . , .      |                    | , ,         |           |              | 181H<br>182H   | Option_REG<br>PCL             |

|                 | movwf                   | OPTION RE                | G           |           |                                       |            |                    |             |           |              | 183H           | STATUS                        |

|                 | BANKSEL                 | PORTA                    |             | nemorv    | bank cor                              | ntaining   | PORTA I            | Register    | (bank 0)  |              | 184H           | FSR                           |

|                 | <i>Di</i> 111022        |                          | ,00.0001    | lieniery  |                                       | itan ing i | ••••••             | logicite.   |           |              | 185H           | SRCON                         |

| ,<br>Main progr | am starts here          |                          |             |           |                                       |            |                    |             |           |              | 186H           | TRISB                         |

|                 |                         |                          | , maya i    | he cent   | opt of TN                             |            | Irogiato           | -           |           |              | 187H           | BAUDCTL                       |

| Main            | movf                    | TMR0,0                   |             |           | ent of TM                             |            | •                  |             |           |              | 188H           | ANSEL                         |

|                 | movwf                   | PORTB                    | ;sent the   | e conten  | t of W re                             | gister to  | LEDS               |             |           |              | 189H           | ANSELH                        |

|                 | goto                    | main                     | ;           |           |                                       |            |                    |             |           |              | 18AH           | PCLATH                        |

|                 | END                     |                          |             |           |                                       |            |                    |             |           |              | 190H -<br>1FFH | GPR<br>16 bytes               |

|                 |                         |                          |             |           |                                       |            | <b>er —</b> Data m | omon hank t | and 3     |              |                | 16 bytes<br>Bank 3            |

|                 |                         |                          | Bit 7       | Bit 6     | Bit 5                                 | Bit 4      | Bit 3              | Bit 2       | Bit 1     | Bit 0        |                |                               |

|                 |                         |                          | RBPU        | INTEDG    | TOCS                                  | TOSE       | PSA                | PS2         | PS1       | PS0          |                |                               |

R/W(1)

R/W(1)

R/W(1) R/W(1) R/W(1) R/W(1) R/W Read/Writable bit; (1) After rest, bit is set;

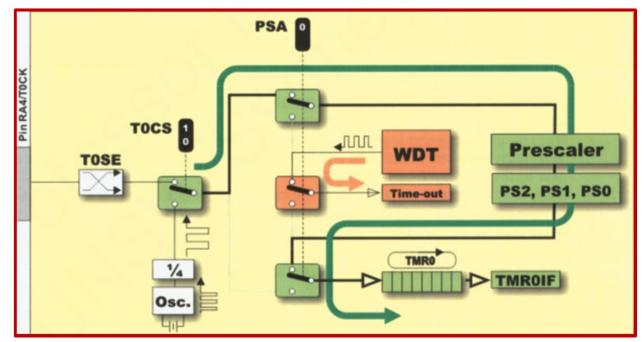

### **TMR0: Timer Mode**

- $\checkmark$  Timer mode is selected by clearing the TOCS bit (OPTION register, bit 5 =0).

- In timer mode, the TMR0 register increments every instruction cycle. As an 8-bit register, TMR0 can count from 00 to FF (255). When it reaches its maximum value, FF, and is incremented further, it rolls over to 00.

- ✓ This register overflow is recorded by the T0IF (Timer0 Interrupt Flag) bit of the INTCON (Interrupt Control) register by being set to 1.

- ✓ The T0IF bit set can trigger an interrupt (known as Timer0 Interrupt), if enabled.

- ✓ The Timer0 interrupt is enabled by setting the T0IE bit (Timer0 Interrupt Enable) of the INTCON register along with the Global Interrupt Enable (GIE) bit.

- ✓ This interrupt would be the indication of the time out and will occur on the every overflow of the TMR0 register.

- ✓ The TOIF bit must be cleared by the interrupt service routine so that the timer interrupt can take place again.

|   |              |               | OPTIO  | N Registe | ⊖ <b>r —</b> Data m | emory bank 1 | and 3  |        |

|---|--------------|---------------|--------|-----------|---------------------|--------------|--------|--------|

|   | Bit 7        | Bit 6         | Bit 5  | Bit 4     | Bit 3               | Bit 2        | Bit 1  | Bit 0  |

|   | RBPU         | INTEDG        | TOCS   | T0SE      | PSA                 | PS2          | PS1    | PS0    |

|   | R/W(1)       | R/W(1)        | R/W(1) | R/Ŵ(1)    | R/W(1)              | R/W(1)       | R/W(1) | R/W(1) |

|   |              |               |        |           |                     | or           |        |        |

|   |              |               |        |           | N Registe           | er           |        |        |

| _ | Bit 7        | Bit 6         | Bit 5  | Bit 4     | Bit 3               | Bit 2        | Bit 1  | Bit 0  |

|   | Bit 7<br>GIE | Bit 6<br>PEIE | Bit 5  |           | •                   |              | Bit 1  | Bit 0  |

- TOCS TMR0 Clock Select bit

- 1 Transition on TOCK1 pin (PA4/RA4 of PORTA); i.e clock mode

- 0 Internal instruction cycle clock (Fosc/4) i.e timer mode

#### **TMR0: Timer Mode**

- ✓ If the clock frequency of PIC16f886 is 4 MHz clock, then the instruction clock will be 1 MHz (1 instruction cycle = 4 clock cycles, for PIC).

- $\checkmark$  The counter would then be clocked every 1 µs exactly.

- ✓ Therefore the Timer0 will take 256  $\mu$ s to count from 00 to FF and then 00.

- ✓ By preloading the TMR0 register with a suitable value, a smaller timer interval (delay) could be selected, with time out indicated by the timer interrupt.

- ✓ For example, if you preload the TMR0 register with the value 200, the Timer0 overflow would occur after 56 µs. (256 µs 200 µs)

- $\checkmark$  An eight bit programmable divider(prescaler) is also available and we can make use of this.

- ✓ The prescaler divides the input frequency by one of eight binary values between 2 and 256.

With 1 MHz instruction cycle, the maximum timer period would be 256 x 256 µs = 65.536 ms, corresponding to the prescaler value of 256.

- ✓ The prescaler values are software selectable through PS0, PS1, and PS2 bits of the OPTION register as explained in the previous slides

- ✓ In order to use the prescaler with the Timer0 module, the PSA bit of the OPTION register must be cleared. If the PSA bit is set, no prescaler will be assigned to the Timer0 module.

$$f_{out} = \frac{f_{clock}/4}{(Prescaler) * (256 - TMR0)} \qquad T_{out} = \frac{1}{f_{out}} \qquad f_{clock} = 4 MHz;$$

*TMR*0: *timer register value*; *Prescalar*: 1 to 256

#### Generating 10 ms Delays usingTMR0

For example, if you preload the TMR0 register with D'100', the Timer0 overflow would occur after 156 μs. (256 μs –156 μs). The maximum timer period with a prescaler value of 64 would be 64 x 156 μs = 9.984 ms, + we need a delay of another 16 μs.

; The Timer0 interrupt is should not be enabled (i.e T0IE bit = 0 of the INTCON register) and the Global Interrupt Enable (GIE) bit should disabled (GIE=0).

| ; initialisat      | ion     |             |        |                      |          |              |                    |              |        |               |

|--------------------|---------|-------------|--------|----------------------|----------|--------------|--------------------|--------------|--------|---------------|

|                    | BANKSEL | OPTION REG  | ;seled | ct Optic             | n regis  | ster to u    | use TM             | 1R0          |        |               |

|                    | Movlw   | B'00000101' |        | ip TMR               | 0        |              |                    |              | =0)    |               |

|                    | -       |             |        | Prescal              |          |              | • •                |              | ,      |               |

| ,                  | movwf   | OPTION REG  | , arra | 10000                |          | , · <b>0</b> | 1,10               | . 0, 1 0     | .,     |               |

|                    |         | of hon_neo  |        |                      | OPTIO    | N Registe    | <b>er —</b> Data m | emory bank 1 | and 3  |               |

|                    |         |             | Bit 7  | Bit 6                | Bit 5    | Bit 4        | Bit 3              | Bit 2        | Bit 1  | Bit 0         |

|                    |         |             | RBPU   | INTEDG               | TOCS     | T0SE         | PSA                | PS2          | PS1    | PS0           |

| ;Main              |         |             | R/W(1) | R/W(1)               | R/W(1)   | R/W(1)       | R/W(1)             | R/W(1)       | R/W(1) | R/W(1)        |

| ,                  | call    | delay10ms   |        | INTCON Register      |          |              |                    |              |        |               |

|                    |         |             | Bit 7  | Bit 6                | Bit 5    | Bit 6        | Bit 5<br>RBIE      | Bit 2        | Bit 1  | Bit 0<br>RBIF |

|                    |         |             | GIE    |                      |          |              |                    |              | INTF   | R/W(x)        |

|                    |         |             | R/W(0) | R/W(0)               | R/W(0)   | R/Ŵ(0)       | R/W(0)             | R/W(0)       | R/W(0) | R/VV(X)       |

| ;delay sub_routine |         |             |        |                      |          |              |                    |              |        |               |

| delay10ms          | movlw   | D'100'      |        |                      |          |              |                    |              |        |               |

| 5                  | movwf   | TMR0        | ·nrelc | ad cou               | nter wi  | ith D'10     | )0"                |              |        |               |

| loop mo            |         |             | •      |                      |          |              |                    | nonod        |        |               |

| loop_ms            | btfss   | INTCON,2    |        | for if tim           |          |              | as nap             | peneo        | i.e iu | IF - I        |

|                    | goto    | loop_ms     | ; loop | ) if not s           | set i.e. | wait         |                    |              |        |               |

|                    | bcf     | INTCON,2    | ;cleai | <sup>r</sup> timer o | overflov | w flag i     | .e. T0I            | F = 0:       |        |               |

|                    | return  | · ·         | ,      |                      |          | 0            |                    | ,            |        |               |

|                    | icturri |             |        |                      |          |              |                    |              |        |               |

### Using TMR0 interrupts

Write an interrupt service routine to increment the number in PORTB by 1, when TMR0 register overflows and causes an interrupt. The maximum timer period would be 256 x 256 µs = 65.536 ms, corresponding to the prescaler value of 256.

| w_temp<br>status_temp     |                                            | equ<br>H'21<br>org<br>goto<br>org<br>goto        | H'20'<br>H'00'<br>start<br>H'04'<br>TMR0_ISR ;;                                                 | go to Interrupt s                                                                          | service                 | 0                         | PIC                                   |                                       |                        |                        |                                 |                         |

|---------------------------|--------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------|---------------------------|---------------------------------------|---------------------------------------|------------------------|------------------------|---------------------------------|-------------------------|

| ;Intialisation<br>start   | BANKSEL<br>clrf<br>BANKSEL<br>clrf         | ANSEL<br>ANSELH<br>TRISB<br>TRISB                | ;set PORTA B                                                                                    | y bank containi<br>to digital by cle<br>y bank containi<br>all outputs                     | aring Al                | NSELF                     | Regis                                 | ster                                  |                        |                        |                                 |                         |

|                           | BANKSEL<br>bcf<br>bcf<br>bsf<br>bsf<br>bsf | OPTION_RE<br>OPTION_RE<br>OPTION_RE              | EG ;select Op<br>EG,5 ;TOCS=0;<br>EG,3 ;Prescale<br>EG,0 ;PS0=1 ;<br>EG,1 ;PS1=1<br>EG,2 ;PS2=1 | r selected                                                                                 | selected                |                           | Bit 6<br>PEIE<br>R/W(0)<br>R/W Read/V | Bit 5                                 | INTE R                 | BIE TOII               | F INTF<br>(0) R/W(0)            | Bit 0<br>RBIF<br>R/W(x) |

| ,<br>,<br>,               | BANKSEL<br>bsf<br>bsf<br>BANKSEL<br>clrf   | INTCON<br>INTCON,5<br>INTCON,7<br>PORTB<br>PORTB | ; T0IE=1 i<br>; Global ii<br>;select memory                                                     | TCON register<br>implies TMR0 c<br>nterrupt enable<br>y bank containi<br>(turn off all LEI | overflow<br>d<br>ng POR | / interru                 | upt is                                | enabled                               | I                      |                        |                                 |                         |

| ;main progra<br>wait_loop | am<br>goto<br>END                          | wait_loop                                        |                                                                                                 | [                                                                                          | Bit 7<br>RBPU<br>R/W(1) | Bit 6<br>INTEDG<br>R/W(1) | Bit 5<br>TOCS<br>R/W(1)               | DN Registe<br>Bit 4<br>TOSE<br>R/Ŵ(1) | Bit 3<br>PSA<br>R/W(1) | Bit 2<br>PS2<br>R/W(1) | and 3<br>Bit 1<br>PS1<br>R/W(1) | Bit 0<br>PS0<br>R/W(1)  |

# Interrupt service routine

| ;Interrupt se<br>TMR0_ISR<br>;<br>; | rvice routine<br>movwf<br>movf<br>movwf | (first save all re<br>w_temp<br>STATUS,W<br>status_temp | egisters)<br>;save current contents of w register in a temporary location 'w_temp'<br>;move the contents of the status register into W register<br>;save the contents of STATUS register in a temporary location 'status_temp'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------|-----------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ;                                   |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;main functio                       |                                         | DODTD                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | BANKSEL<br>incf                         | PORTB<br>PORTB                                          | ; increment the content of PORTB by 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                     | BANKSEL                                 | INTCON                                                  | ;select the databank memory containing INTCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                     | bcf                                     | INTCON,2                                                | ; clear interrupt flag bit T0IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -<br>,                              |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;                                   |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;Restore all                        | -                                       |                                                         | W wetrieve the CTATUC register content coved in terms are a leasticn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                     | movf                                    |                                                         | W ;retrieve the STATUS register content saved in temporary location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                     | movwf                                   | STATUS                                                  | ; put it back in the STATUS register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                     |                                         |                                                         | ons , before returning from the service routine should not affect the STATUS register.<br>s as they do not affect the STSTUS register (see instruction set sheet)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ,                                   | swapf                                   | w temp,1                                                | ;the upper and lower nibbles are exchanged in w-temp and result placed in w-temp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                     | swapf                                   | w_temp,0                                                | ;the upper and lower nibbles are exchanged in w-temp and result placed in W reg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -                                   |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | bsf                                     | INTCON,7                                                | ;Global interrupt enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                     | retfie                                  |                                                         | ;return from the interrupt service routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ,                                   | END                                     |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | END                                     |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | Bit 7                                   | Bit 6 Bit 5                                             | INTCON Register      OPTION Register – Data memory bank 1 and 3        Bit 6      Bit 5      Bit 1      Bit 0      Bit 7      Bit 6      Bit 5      Bit 2      Bit 1      Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                     | GIE                                     | PEIE TOIE                                               | INTE RBIE TOIF INTF RBIF RBIF RBPU INTEDG TOCS TOSE PSA PS2 PS1 PS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                     | R/W(0)                                  | R/W(0) R/W(0)                                           | R/W(0)      R/W(0)      R/W(0)      R/W(0)      R/W(x)      R/W(1)      R/W(1)< |

R/W Read/Writable bit; (0) After rest, bit is cleared; (x) After reset, bit is unknown

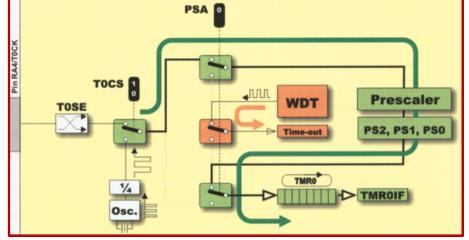

# Watchdog Timer (WDT)

- One of the major functions of a watchdog timer is to automatically reset the microcontroller in the event of a crash.

- The watch-dog timer built-in to the PIC16f886 runs with its own RC oscillator (independent of external clock) and has a typical minimum time-out period of 18 milliseconds. There is a programmable prescaler (which divides the RC clock) that can multiply this period by 128 (max) to give a total time-out period of 2.3 secs, which is good for most applications.

- ✓ When the Watchdog Timer (WDT) is enabled, a counter starts at 00 and increments by 1 until it reaches FF. When it goes from FF to 00, the PIC micro will be reset.

- The only way we can stop the WDT from resetting the PIC is to periodically reset the WDT back to 00 within the program.

- ✓ The instruction for clearing the WDT is 'clrwdt'

- ✓ If the program does get stuck for some reason, the WDT will then reset the PIC, causing our program to restart from the beginning.

# Watchdog Timer (WDT)

- ✓ Hopefully when the PIC restarts whatever condition led to the crash will have gone away and the PIC will resume its normal operation.

- Note that the prescaler is not readable or writeable. When assigned to the TMR0 module, all instructions writing to the TMR0 register will clear the prescaler

- ✓ When the prescaler is assigned to WDT, a 'clrwdt' instruction will clear the prescaler along with the WDT.

- ✓ When changing the prescaler from Timer0 to the WDT module or vice versa care must be taken and a sequence of instructions must be executed (Ref: microchip data sheet)

#### **Laboratory Activities**

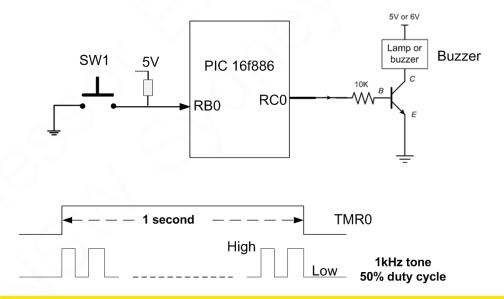

Activity 8: Intrusion Warning System

- Write an assembly language program for an intrusion warning system, that uses interrupts on the PIC16F886 microcontroller to sound an 1000 Hz tone for 1 second, whenever a door sensor (SW1) connected to RB0 is closed (i.e., there is an intrusion through the door) (see figure below).

- The 1 second time-out must be implemented using the TMR0 register overflow interrupt. Also calculate the total amount of program memory space required for the interrupt routine, in terms of bytes, occupied.

- Note that you are required to include a switch de-bouncing routine.

#### **ELEC2117: References**

- 1. Designing Embedded Systems with PIC Microcontrollers Tim Wilmshurst, Elsevier, 2010

- 2. PIC Microcontrollers –Free online book mikroElektronika ; http://www.mikroe.com/products/view/11/book-pic-microcontrollers/

- 3. PIC 16F886 Data Sheet (2007), Microchip Technology; www.microchip.com